Delancy7

1 mW

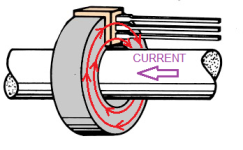

I've been using controllers to understand FOC motor control, and these small, cheap controllers typically implement motor phase current sensing as low-side shunts on two or three of the phases. This works, to an extent, but seems very noisy and not the best way to sense current, and is probably implemented on cheap controllers because of cost considerations.

I plan to create my own controller for test purposes and want to use a better method of motor phase current sensing. What's the best practice for motor current sensing in this application? This controller will be a one-off and cost won't be a consideration--I'd prefer a robust and accurate method as opposed to something cheap to implement.

The motors I'm using are small, and typical currents will be no more than 5-10 amps at 24v.

I plan to create my own controller for test purposes and want to use a better method of motor phase current sensing. What's the best practice for motor current sensing in this application? This controller will be a one-off and cost won't be a consideration--I'd prefer a robust and accurate method as opposed to something cheap to implement.

The motors I'm using are small, and typical currents will be no more than 5-10 amps at 24v.