mxlemming

100 kW

- Joined

- Jul 17, 2020

- Messages

- 1,120

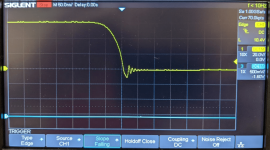

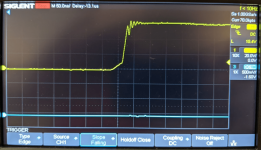

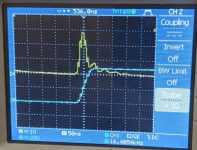

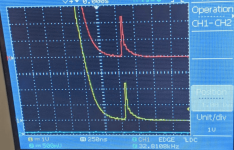

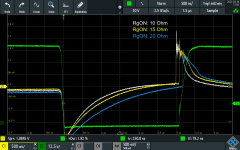

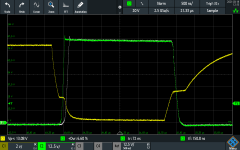

marcos said:A switching trace at 4A is worthless, you want to find how bad your voltage overshoot is, and V=L*di/dt. If your "i" is like 2% of your worst case scenario, then your measured overshoot is likely in the 2% range of what you will really have down the road.mxlemming said:peters said:Really clean signals, but at how much current?

Current is only about 4A on my desk with the small motor. It's quite hard for me to get high currents at my desk with an EBike motor, they generate a load of torque, and when spinning have enough energy to grind holes in my desk.

That's why so much effort is spent getting the test rig right, a double pulse test doesn't need a high power supply, in fact you typically just charge the DC link and disconnect the power supply right before the test, especially when you want to make sure the short circuit protections can trip with the energy of the DC Link alone.

OK,

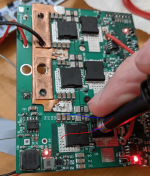

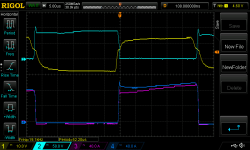

I am currently severely time and budget limited, so will not imminently have time to code or rewire for double pulse test, but I do have time for this:

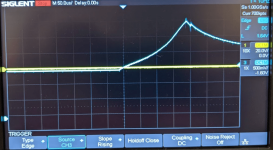

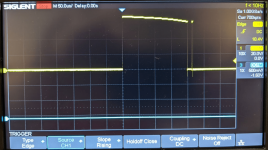

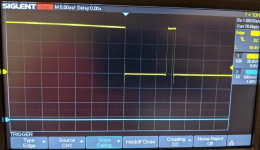

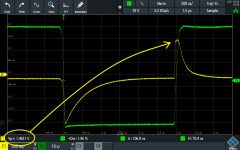

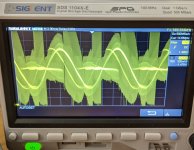

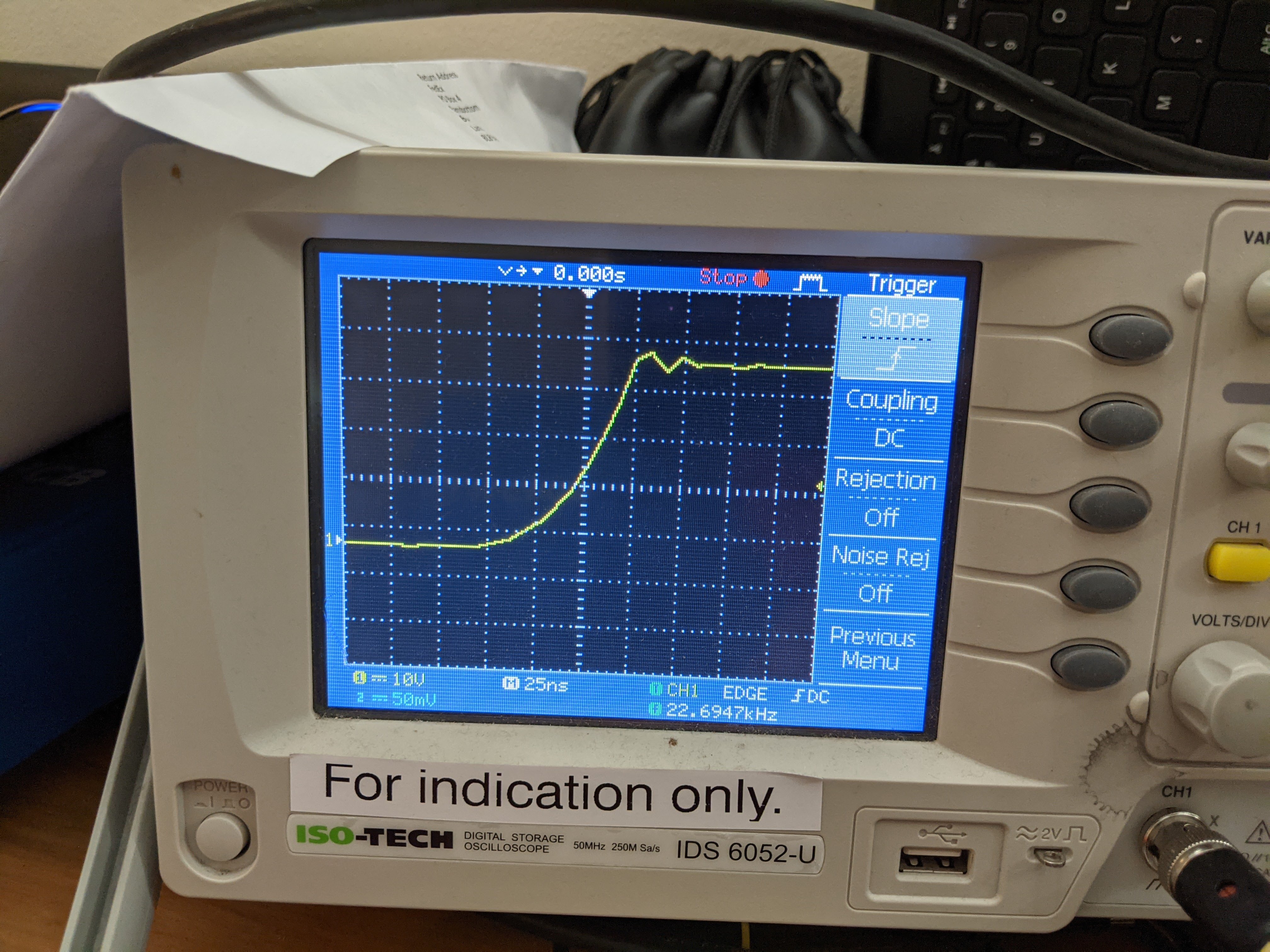

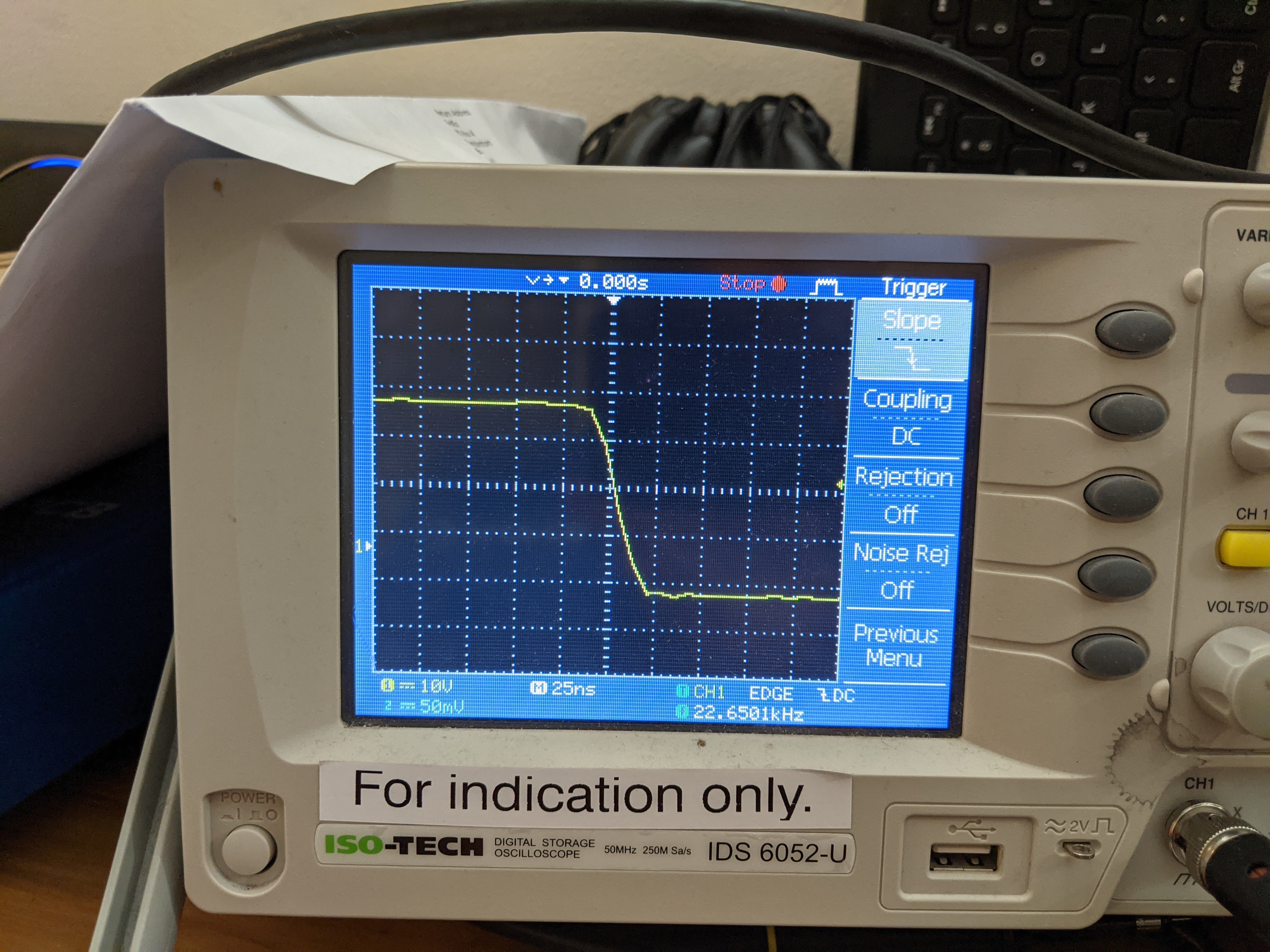

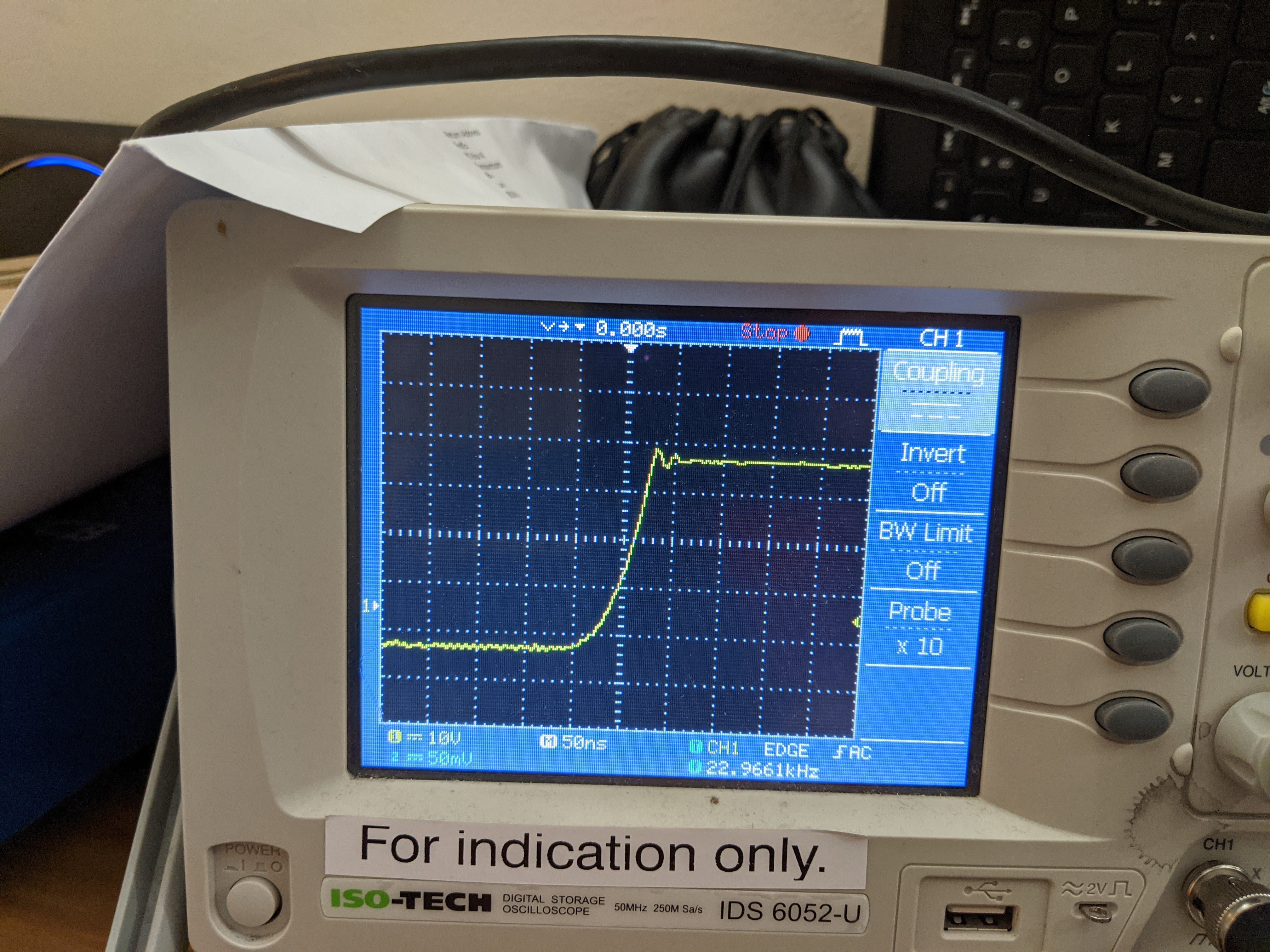

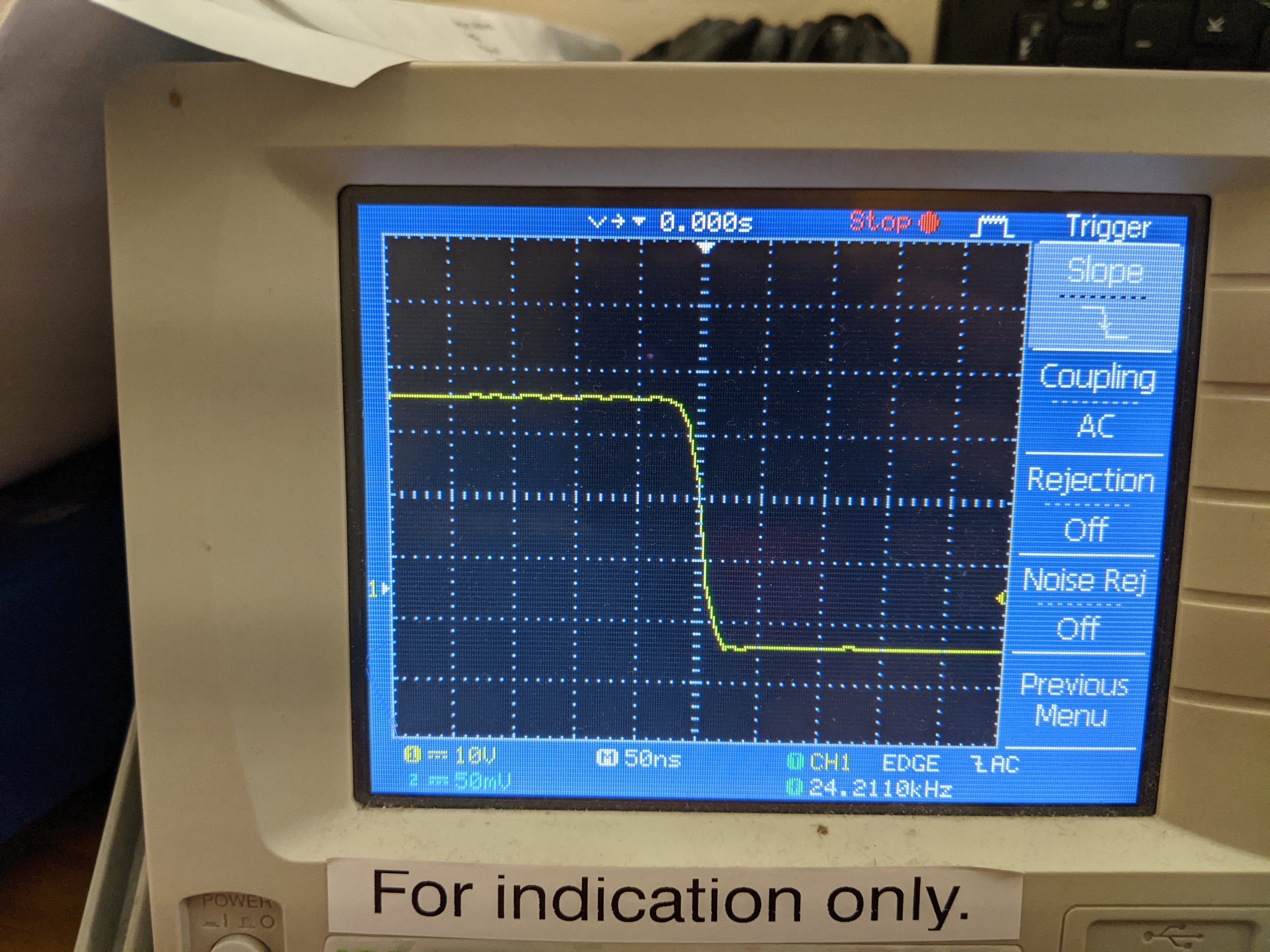

70A Id, 5A Iq, which corresponds to about 60A phase (IIRC, the conversion ratio from the Clark/park gives (sqrt6)/2).

At this power, the PSU is sinking >150W into the PCB/motor (the gauge fluctuates a lot around this value). The motor gets hot quite fast; over about a minute. The PCB gets... Warmish... FETs probably approaching 60 degrees with no heatsink after a minute or so. If I increase Id current any more, the PSU just starts to crap out. It's only got a 250W mains

Motor phase resistance is 40mohm, so sinking ~150W implies something in the region of 50-60A. Current traces on the shunts show current sin wave peaks are ~81A, so RMS current is ~58A.

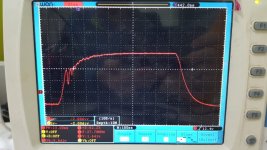

Not really much more ringing or weirdness at this higher current. I really need a more expensive scope than this 250$ piece of junk from the early 2000s though. Looking longingly at a Keysight 200MHz 4 channel job... Think I might take the plunge after a few pay cheques.