rhitee05 said:

I don't want to be the wet blanket, but I think we should be careful about spec creep here. There is a very fine line between a flexible, versatile design and a monstrosity where people are paying for 100 features they don't need to get the 5 they do.

I've seen numerous projects here at school. The ones that succeed usually start with modest aims, then over time improve to perfection. The ones that aim for the moon often remain on paper. It of course comes down to the experience of the builder or builder team.

Here on ES we have already had people selling kits and others successfully building them.

Not much more difficult would be to start from a Xiechang, and say duplicate the design Jeremy has posted for low volts, high current 6FET. The builder has to buy the parts, assemble and test. One can imagine other variations of the basic 6FET board for different apps.

Next step would be to add an intermediate driver circuit board to allow higher power FET stages. I'm anxiously waiting for LFP's results on this. Simple versions of these could be PCB layouts for PCB soldered FETs on the diver board. More elaborate would be to specially construct high power buses with short runs, good geometry and minimal inductance etc, so the power routing is optimized and decoupled from the drivers. Hence a high power controller would be a three-layer sandwich: 1/ the Xieachang board, 2/ the driver board, 3/ and finally the power FETs and bus bolted directly to a heat sink.

I'm curious how much of the scaling problem with 2,3,4 parallel FETs that we see on the Infineon controllers sold here can be avoided with better PCB design. The infineon 12 and 18 FET "all FET's in a row" design seems like the worst of the bunch. BMC's 4110 50A controller looks a bit more promising in this respect. Has anyone tried modding that? What MCU? How many electrical rpm does it seem to handle? I need a candidate to mod for my 5-6kW Astro build, but I'm going to push the astro to 10-15k rpm, so I'm looking for 150,000+ electrical rpm.

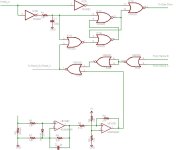

Designing the MCU part from scratch I suspect will be a whole other can of worms. Newark/Farnell had an article on it in their monthly magazine about a year ago. I've emailed them numerous times for an electronic pdf copy to post to ES, but the sales and interned dudes are stumped by any out of the ordinary request... I'll see if I can look up the reference. I think I posted it before.