nieles

10 kW

hi,

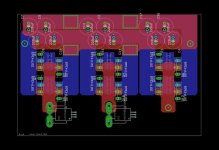

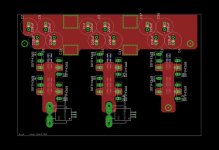

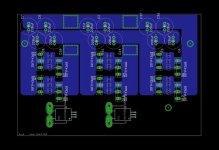

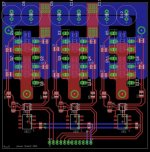

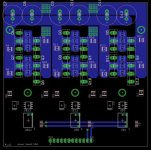

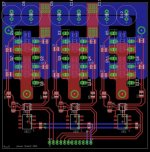

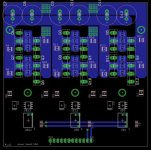

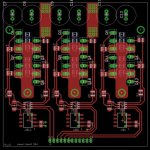

i have been designing a Powerstage PCB for my controller build using the controller chip from Lebowski.

This is what i have so far:

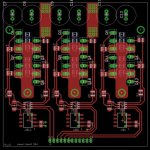

and the schematics (its a little messy, i still need to clean it up)

as you can see i have been studying this thread 8) : http://endless-sphere.com/forums/viewtopic.php?f=2&t=35071&hilit=water+cooled

few questions:

-What kind of copper pour should i place on the bottomside of the PCB where the fet drivers are located? for optimal noise imunity

-what would be the best way to connect the High power side GND to the GND from the drivers? would it good to use a low value resistor beteen the two grounds?

-i have a dc-dc converter for charging my bootstrap capacitor, are there any drawbacks (other than cost) for using one instead of a diode? in the application notes i have read they only mention the advantages for using one, and not the drawbacks.

Let me know what you guys think!

i am open to suggestions to improve this design

i have been designing a Powerstage PCB for my controller build using the controller chip from Lebowski.

This is what i have so far:

and the schematics (its a little messy, i still need to clean it up)

as you can see i have been studying this thread 8) : http://endless-sphere.com/forums/viewtopic.php?f=2&t=35071&hilit=water+cooled

few questions:

-What kind of copper pour should i place on the bottomside of the PCB where the fet drivers are located? for optimal noise imunity

-what would be the best way to connect the High power side GND to the GND from the drivers? would it good to use a low value resistor beteen the two grounds?

-i have a dc-dc converter for charging my bootstrap capacitor, are there any drawbacks (other than cost) for using one instead of a diode? in the application notes i have read they only mention the advantages for using one, and not the drawbacks.

Let me know what you guys think!

i am open to suggestions to improve this design