ARod1993

100 W

I couldn't sleep and so I took a whack at designing a power board for a fairly large motor controller. The board itself is a 6FET power board; the idea would be to parallel several of them to create a 150V, 400- to 600A-capable controller. The board takes in a differential PWM signal and isolated 15V rail for each phase, as well as non-isolated 5V and 15V rails for control logic and low-side drive, and uses these isolated half-bridge drivers to drive each transistor pair. I went with the HSOF-8 package for the transistors (also known as TO-leadless) mostly out of curiosity, but primarily because the AOTL66518 caught my eye; it claims 214A at 150V, which is likely fairly optimistic. That said, 150V at 100A per board isn't a terribly bad deal at $7 per FET, and these look like they can switch fast (back of the envelope says 115nC gate charge with a 4A gate driver is ~30ns, so switching losses at 100kHz (200kHz center-aligned) would only be about 40W per device (add in the conduction losses and you're at about 80W per device, which is 95% efficient, and 100kHz is fast enough to drive controller-eating motors).

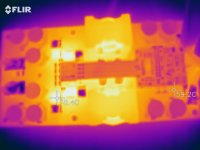

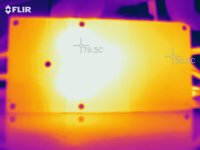

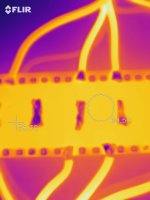

The power pass is designed for fairly low inductance; the positive and negative buses are on the top and bottom of the board, with interlocking comb teeth to each transistor. The phase leads are intended to attach via busbar perpendicular to the main power bus (the two holes between each transistor pair are the mounting points for that); in a multistage controller the boards would be placed next to each other and a single busbar would connect to all the boards on each phase lead. For bus capacitance I went with 1640uF bulk electrolytic, and then 2.2uF ceramic very close to the ground pad of each FET; I'd love comments and critique of the layout! Here's a few shots of the 3D board view and the layout:

The power pass is designed for fairly low inductance; the positive and negative buses are on the top and bottom of the board, with interlocking comb teeth to each transistor. The phase leads are intended to attach via busbar perpendicular to the main power bus (the two holes between each transistor pair are the mounting points for that); in a multistage controller the boards would be placed next to each other and a single busbar would connect to all the boards on each phase lead. For bus capacitance I went with 1640uF bulk electrolytic, and then 2.2uF ceramic very close to the ground pad of each FET; I'd love comments and critique of the layout! Here's a few shots of the 3D board view and the layout: