Lebowski

10 MW

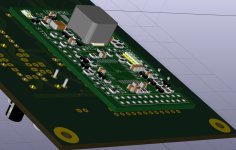

minimum said:Gate drivers on separate PCB, on top (or underneath, depending on the POV) of FET PCB?

Gate drivers in SMD underneath the current sensors... but it should be an easy to solder board for everyone

minimum said:Gate drivers on separate PCB, on top (or underneath, depending on the POV) of FET PCB?

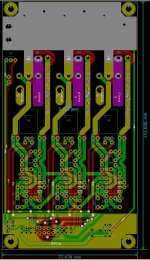

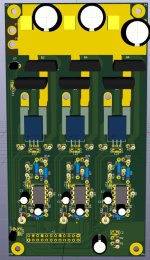

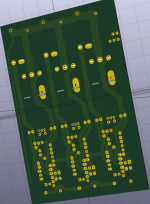

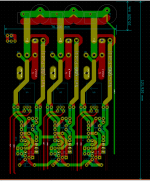

Lebowski said:I hear your comments... Swapping the place of the gate drivers and current sensors:

pic1.png

pic3.png

pic2-800x800.png

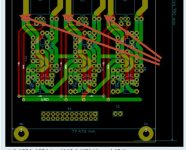

I like the straight shot of the output to the current sensors. If I only use the top layer for the high current path, then I can route the gate signals underneath the current sensors.

What I don't really like is the long gate driver wires. An online inductance calculator tells me that the inductance fo two flat 2mm wires spaced at 2.54mm is 16nH per cm (so 160nH for 10 cm). The Ciss of the Fets is 7 nF (for ITXH180) or 20nF (for 4468's). The turn-off gate resistor is between 4.7 and 10 Ohm.

Damping is 0.5 * R * sqrt(C/L).

So the 4468 with 4.7 Ohm gives a damping of 0.83

The ITXH180 with 10 Ohm gives a damping of 1.05

Both numbers do not impress me, I would like to have had 2 or higher... the cause is of course the high wiring L.

P.S. no clue why some pictures show up bigger than others... even when I make all 800 pixels wide they still show up differently ?

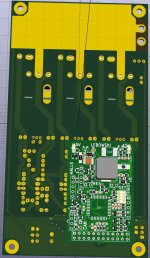

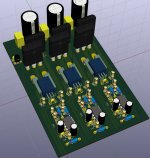

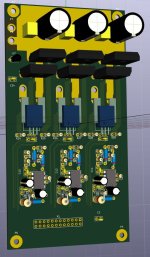

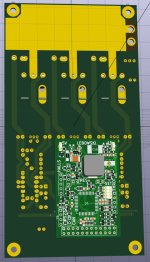

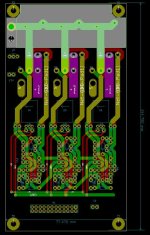

Lebowski said:Think I've got it now:

pic1-modified.jpg

pic2.png

pic3.png

The 'clou' it that the gate drive lines are no longer 2mm track spaced 2.54mm (with a 16nH/cm inductance) but now are 3mm wide track opposite each other on both layers of the PCB (giving a 6.7nH/cm inductance).

This reduced inductance can be used to space the gate drivers further away, making room for the current sensors.

The output of the FETs it now a straight shot on the top metal to the current sensor. The output can be taken at the other side of the current sensors, either top or bottom of the PCB. Regarding the bottom, the hole at the current sensor terminal is now 1.6mm (same as FETs), but maybe 2.5 or 3 mm should be better...

Animalector said:Ok good to know... I was under the impression that noise / interference would be a problem as well.

So conceptually, If I keep the gate signal closely coupled with its reference (either GND for low side and phase-out for high side) by having the reference immediately below, and possibly beside as well? It should be right... Yes?

Thanks

Andy