glenn0010

100 W

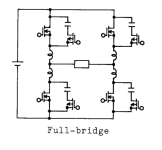

Hi All I am desgigning my own 3 phase motor controller. I want to implement a snubber circuit to Protect the FETs. I will use and RC snubber circuit since it is simple and effective, even though it has quite low efficiency (approx 40%-60%).

I have found this application note which is great and guides you through the process of designing the snubber effectively. I have understood all the process however I still have some unanswered questions.

https://assets.nexperia.com/documents/application-note/AN11160.pdf

1 - Do the snubber capacitors (i.e. C add for testing and the final Cs) need to be LOW ESR etc since they are more expensive. I think so as the ringing frequencies can be in the MHz ranges so an electrolytic will be too 'slow' to react.

2 - How do you calculate the power rating that the resistor is required to be since it dissipates heat in it?

3 - In page 8 the application note states the following :

"As seen in Figure 6, the snubber has almost eliminated the ringing in the VDS waveform.

This technique could also be applied to the MOSFET in the Q2 position."

I am assuming that from that statement I need a subber across both the high side and low side FETs at the same time. If this is correct, can I assume the snubber values are the same as those calculated for the high side FETs since the positioning on the PCB of the FETs maybe different hence leading to a different Llk (stray inductance). However I think this would have minimal affect.

Thanks for your help !

I have found this application note which is great and guides you through the process of designing the snubber effectively. I have understood all the process however I still have some unanswered questions.

https://assets.nexperia.com/documents/application-note/AN11160.pdf

1 - Do the snubber capacitors (i.e. C add for testing and the final Cs) need to be LOW ESR etc since they are more expensive. I think so as the ringing frequencies can be in the MHz ranges so an electrolytic will be too 'slow' to react.

2 - How do you calculate the power rating that the resistor is required to be since it dissipates heat in it?

3 - In page 8 the application note states the following :

"As seen in Figure 6, the snubber has almost eliminated the ringing in the VDS waveform.

This technique could also be applied to the MOSFET in the Q2 position."

I am assuming that from that statement I need a subber across both the high side and low side FETs at the same time. If this is correct, can I assume the snubber values are the same as those calculated for the high side FETs since the positioning on the PCB of the FETs maybe different hence leading to a different Llk (stray inductance). However I think this would have minimal affect.

Thanks for your help !