Okey. I read your post concerning desat calculation.

https://endless-sphere.com/forums/viewtopic.php?f=30&t=61937&p=940576&hilit=desaturation#p940576

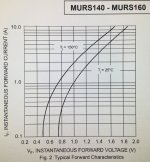

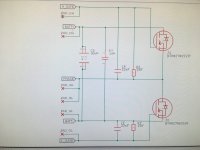

As the current which goes from td350e desat pin is 250uA I see that it is curcial to read voltage from zener diode datasheet when conducts this amount of current. From datasheet this small amount of current could not be read.

If I choose to order new diode it will take a long time before it comes. Maybe I could use one allready available. I have diodes with 5.1v 5.6V and 6.2V.

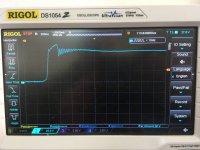

I can place on of them 5.6V in desat circuit and measure voltage across it with scope. Fet will work with some average current level. Will this be good result concerning diode voltage at 250uA current?

https://endless-sphere.com/forums/viewtopic.php?f=30&t=61937&p=940576&hilit=desaturation#p940576

As the current which goes from td350e desat pin is 250uA I see that it is curcial to read voltage from zener diode datasheet when conducts this amount of current. From datasheet this small amount of current could not be read.

If I choose to order new diode it will take a long time before it comes. Maybe I could use one allready available. I have diodes with 5.1v 5.6V and 6.2V.

I can place on of them 5.6V in desat circuit and measure voltage across it with scope. Fet will work with some average current level. Will this be good result concerning diode voltage at 250uA current?