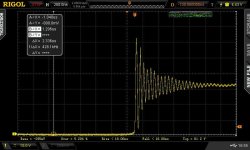

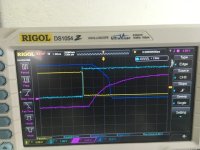

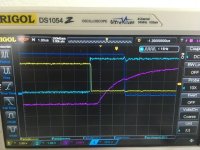

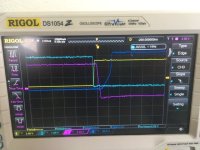

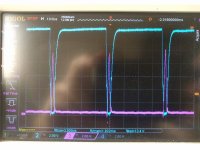

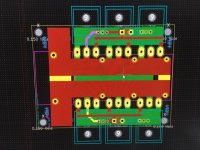

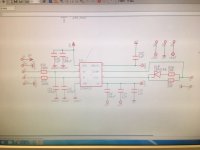

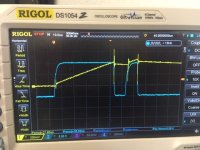

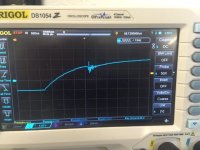

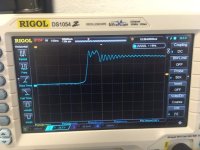

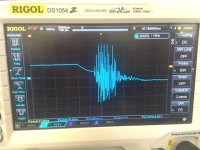

Yes but wouldn’t high inductance motors “eat” these harmonics so they will not reflect current and torque. Currently am buliding this for motors having from 1mH to 2.5mH. So current controller would not have to fight with such disturbances. I see that problem coiuld be with low inductance motors. Anyway I plan to redesing power stage but what inductance of power stage is good to supress these low freq oscillations? In earlier power stage(two copper sheets and capton tape between) it was measured about 20nH and in some point I tested with only PP caps and still there was low freq oscillations.zombiess said:With enough capacitance added the frequency can be made lower, but you will still be introducing additional frequency harmonics into your load.

I saw couple of commercial products of dc drivers for cnc machines they use combination of higher value of electrolytic capacitor with low value of PP or poliester cap. Could the issue of low freq oscillations in my case be from transformer power supply(and its caps and internal inductance)? I am thinking that batteries you used for your testing acting like “perfect” power source compare to my power supply with transformer, rectifier and electrolytic caps.

You answerd.zombiess said:what do you mean?