Lebowski

10 MW

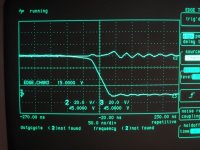

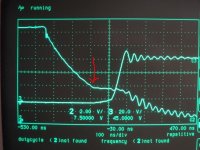

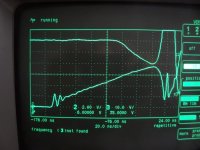

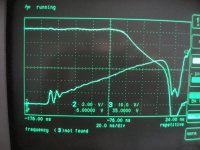

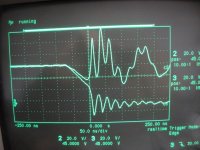

I'm starting this thread because of my suggested gate-drain RC network in Arlo's output stage thread. It seems to work well

in Arlo's 15kW controller so I wanted to investigate this technology myself. First measurements showed something

different from what i expected, so all the more reasons for an in-depth look. I'll probably update this first post of the thread

as I go along, not to have information lost and impossible to find somewhere in the middle of the thread.

Plus the weather here is crap so nothing better to do :?

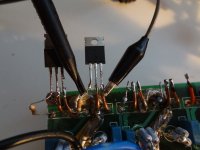

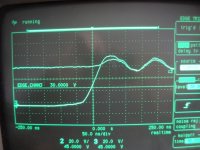

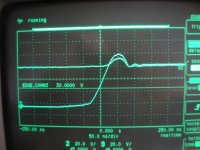

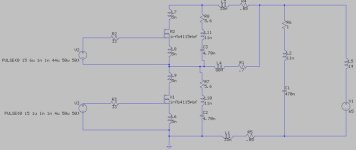

This is the output stage at the start:

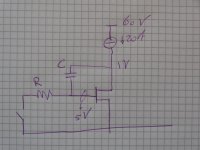

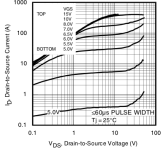

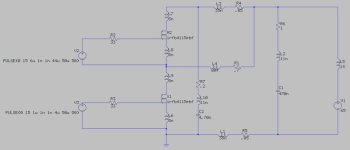

Two 4115's driven by a IRS2186 gate driver IC. The snubber components are disconnected. As a supply I'm using a 60V 2.5A

lab supply. I will only look at one output stage and use the PWM test function of my controller IC as the signal source.

The load is a big inductor and a few power resistors:

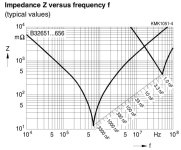

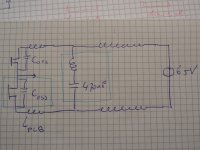

Because I don't really like the 'just add more capacitors' approach I use only two capacitors on the supply rail:

The caps are on the right, the big black cilinder is a 220uF cap with probably quite a high series inductor, underneath

it (the blue block) is a 470nF low inductance capacitor.

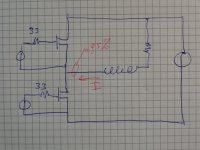

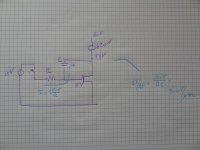

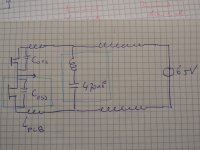

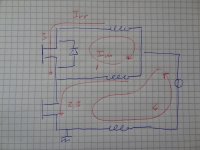

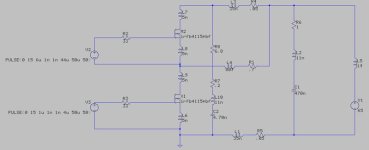

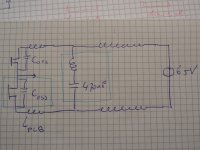

This is the schematic of what we have. On the right is the power supplies, which is connected with two long wires to the PCB. The long wires

represent quite some inductance. The 470nF capacitor is added to short out this inductance so the power stage doesn't see it, but it's not

100% succesfull at doing this as it has a small internal inductance itself. Going left from the 470nF we get the inductance of the PCB traces and

then the two 4115's.

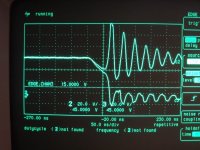

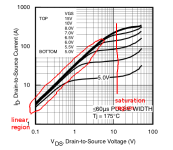

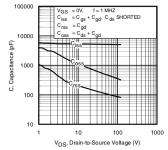

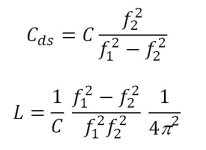

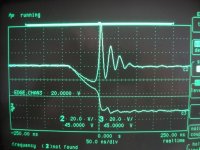

The difficulty is now that when the output to the motor switched from rail-to-rail, the PCB inductors together with the output capacitor C_oss (of the

switched off transistor) causes ringing which overvolts the transistors and blows them up. Two strategies exist to prevent this. So far I've always used

the drain-source snubber approach, where an RC series network is placed across the drain-source of the transistors. The values of the RC are

chosen such that the ringing is greatly dampened. So, kinda the 'switch hard, ringing will be there but lets deal with it' approach.

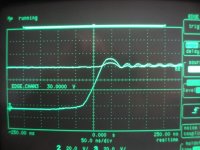

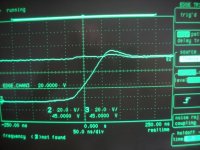

The other approach, which is the subject of this thread, is the 'switch gently so no ringing will occur'. More technical, switching hard puts a whole

spectrum of frequencies on the output, the LC filter of the supply/C_oss selects the one it likes and amplifies it. Switching softly means the LC_preferred

frequency is greatly reduced in the output, so that there's not a lot going on at the LC frequency and hardly anything present to ring with.

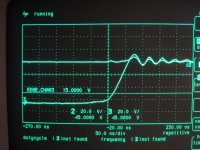

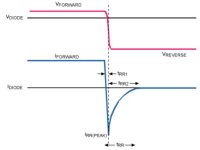

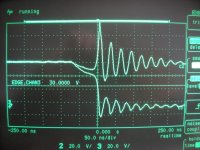

First order of business is to see which transistor determines what. We have rising and falling edges in the output signal, and the transistor

in control depends on the direction of the motor current.

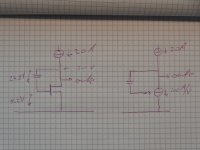

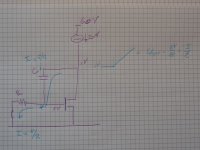

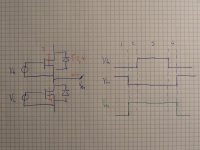

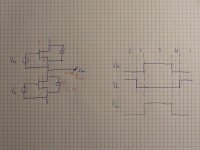

The picture shows the two output stage transistors, the high side being controlled by driver voltage V_h, the low side transistor controlled by V_l.

On the right you see the no-overlapping waveforms (with the deadtime) of V_h and V_l. There are 4 phases the output stage goes through during

one cycle of the PWM frequency, marked 1 to 4. The output to the motor is marked V_m. In this first picture the motor current I_m flows into the

controller as marked by the arrow.

During phase 1 with V_l high, the low side is on and carrying all the motor current. When the low side switches off I_m has to keep flowing (because

of the motor inductance, which acts as a current source), the only path open to it is via the high side diode (phase 2). When going from phase 1 to

phase 2 the motor voltage goes from low to high, as the motor terminal is kind off shorted to the high supply via the diode in the high side transistor.

The slope on V_m when going from phase 1 to 2 is controlled by the switching off of the low side transistor, so it is controlled by whatever gate resistor

etc we have in the low side.

Going into phase 3, the current is transferred from the high side diode to the high side FET. At the motor terminal you don't really see this as it

stays connected to the high supply. This means that the high side FET can switch slow or super fast, we just don't see it, the motor terminal

stays at the high voltage.

Goind to phase 4, the high side FET is switched off and the current is transferred to the high side diode. Again, this is not visible at the motor terminal

so, whether the high side switches slow or fast, we don't see it.

Going from 4 to 1, the current is transferred to the low side FET, the motor terminal voltage V_m goes low. The slope of V_m depends on how fast

or slow the low side switches.

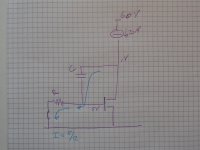

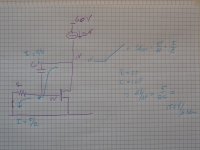

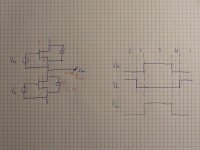

The situation changes when the direction of the motor current is reversed.

The reasoning is the same as the previous picture, except this time all the transitions of V_m are controlled by the high side transistor.

So, to summarize, with current going into the motor the rising/falling edges of V_m (and all the ringing) are determined by the high side FET, with

current coming from the motor flowing into the controller thre rising/falling edges of V_m are determined by the low side FET. It is important to

realise it is not as straightforward as saying the high side FET determines the rising edges iof V_m and the low side FET the falling edges !

As an intermezzo, notice how the effective width of the V_m signal depends on the motor current, dependent on I_m's direction V_m is wider

or narrower by an amount of twice the deadtime. Notice also that it opposes I_m, when delivering I_m to the motor V_m is narrow (so in

effect represents a lower voltage). This is as if there is a 'virtual resistor' in the system. A larger deadtime represents a larger resistor... not good.

in Arlo's 15kW controller so I wanted to investigate this technology myself. First measurements showed something

different from what i expected, so all the more reasons for an in-depth look. I'll probably update this first post of the thread

as I go along, not to have information lost and impossible to find somewhere in the middle of the thread.

Plus the weather here is crap so nothing better to do :?

This is the output stage at the start:

Two 4115's driven by a IRS2186 gate driver IC. The snubber components are disconnected. As a supply I'm using a 60V 2.5A

lab supply. I will only look at one output stage and use the PWM test function of my controller IC as the signal source.

The load is a big inductor and a few power resistors:

Because I don't really like the 'just add more capacitors' approach I use only two capacitors on the supply rail:

The caps are on the right, the big black cilinder is a 220uF cap with probably quite a high series inductor, underneath

it (the blue block) is a 470nF low inductance capacitor.

This is the schematic of what we have. On the right is the power supplies, which is connected with two long wires to the PCB. The long wires

represent quite some inductance. The 470nF capacitor is added to short out this inductance so the power stage doesn't see it, but it's not

100% succesfull at doing this as it has a small internal inductance itself. Going left from the 470nF we get the inductance of the PCB traces and

then the two 4115's.

The difficulty is now that when the output to the motor switched from rail-to-rail, the PCB inductors together with the output capacitor C_oss (of the

switched off transistor) causes ringing which overvolts the transistors and blows them up. Two strategies exist to prevent this. So far I've always used

the drain-source snubber approach, where an RC series network is placed across the drain-source of the transistors. The values of the RC are

chosen such that the ringing is greatly dampened. So, kinda the 'switch hard, ringing will be there but lets deal with it' approach.

The other approach, which is the subject of this thread, is the 'switch gently so no ringing will occur'. More technical, switching hard puts a whole

spectrum of frequencies on the output, the LC filter of the supply/C_oss selects the one it likes and amplifies it. Switching softly means the LC_preferred

frequency is greatly reduced in the output, so that there's not a lot going on at the LC frequency and hardly anything present to ring with.

First order of business is to see which transistor determines what. We have rising and falling edges in the output signal, and the transistor

in control depends on the direction of the motor current.

The picture shows the two output stage transistors, the high side being controlled by driver voltage V_h, the low side transistor controlled by V_l.

On the right you see the no-overlapping waveforms (with the deadtime) of V_h and V_l. There are 4 phases the output stage goes through during

one cycle of the PWM frequency, marked 1 to 4. The output to the motor is marked V_m. In this first picture the motor current I_m flows into the

controller as marked by the arrow.

During phase 1 with V_l high, the low side is on and carrying all the motor current. When the low side switches off I_m has to keep flowing (because

of the motor inductance, which acts as a current source), the only path open to it is via the high side diode (phase 2). When going from phase 1 to

phase 2 the motor voltage goes from low to high, as the motor terminal is kind off shorted to the high supply via the diode in the high side transistor.

The slope on V_m when going from phase 1 to 2 is controlled by the switching off of the low side transistor, so it is controlled by whatever gate resistor

etc we have in the low side.

Going into phase 3, the current is transferred from the high side diode to the high side FET. At the motor terminal you don't really see this as it

stays connected to the high supply. This means that the high side FET can switch slow or super fast, we just don't see it, the motor terminal

stays at the high voltage.

Goind to phase 4, the high side FET is switched off and the current is transferred to the high side diode. Again, this is not visible at the motor terminal

so, whether the high side switches slow or fast, we don't see it.

Going from 4 to 1, the current is transferred to the low side FET, the motor terminal voltage V_m goes low. The slope of V_m depends on how fast

or slow the low side switches.

The situation changes when the direction of the motor current is reversed.

The reasoning is the same as the previous picture, except this time all the transitions of V_m are controlled by the high side transistor.

So, to summarize, with current going into the motor the rising/falling edges of V_m (and all the ringing) are determined by the high side FET, with

current coming from the motor flowing into the controller thre rising/falling edges of V_m are determined by the low side FET. It is important to

realise it is not as straightforward as saying the high side FET determines the rising edges iof V_m and the low side FET the falling edges !

As an intermezzo, notice how the effective width of the V_m signal depends on the motor current, dependent on I_m's direction V_m is wider

or narrower by an amount of twice the deadtime. Notice also that it opposes I_m, when delivering I_m to the motor V_m is narrow (so in

effect represents a lower voltage). This is as if there is a 'virtual resistor' in the system. A larger deadtime represents a larger resistor... not good.