hy guys,

i'm back with measurements, i have some good news and some confusing ones, so here it is:

the controller spins the motor,

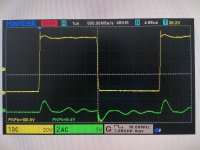

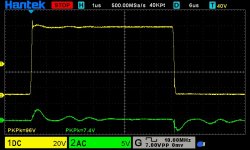

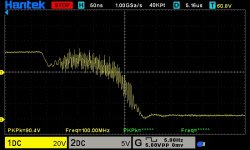

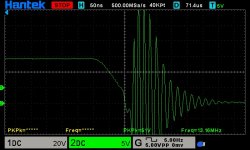

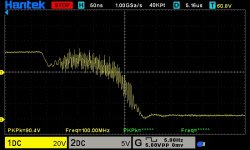

i made the double pulse test as before, the setup is as follows, low side pulsed, 90v bus, 10uH 6mohm inductor (the motor), snubbers with 0.75 dumping on Ls and Hs, gates tied together thru 1 ohm resistor then Rgate 2.2R for Ton and Toff, with active miller clamp, without 2 level turn off, desat is used (5v1 zenner) but not configured right at this time (needs lower zenner voltage), yellow trace is Vds greed trace is Vgs.

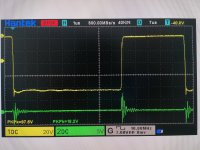

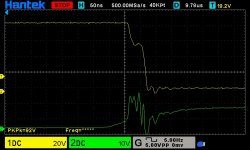

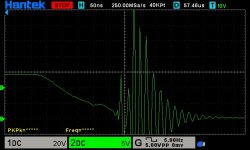

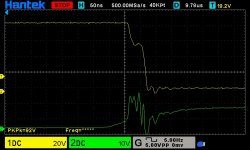

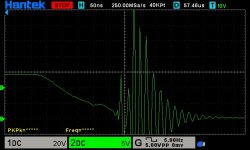

i started testing with some short 600ns pulses, all was ok-ish, (only this shot has Vgs yellow trace), i say ok-ish because Vgs rises nicely then once is up it has a sharp short drop to 0 then back up, that drop does not seem to be in the miller plateau but as you will see in further shots it is located in the region the Vds drops down fast, so i think when Vds drops fast it pulls down the gate voltage or something, with the previous gate drivers in that same position was some crazy ringing.

the 600ns Vgs shot.

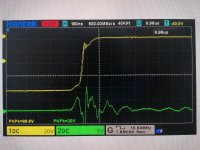

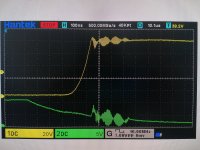

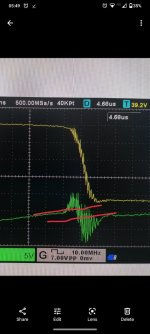

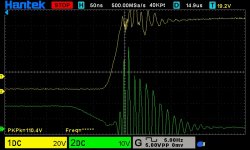

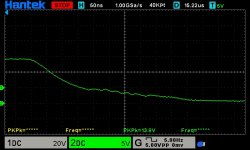

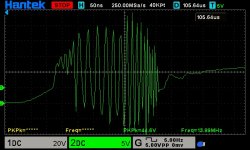

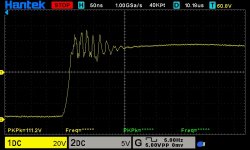

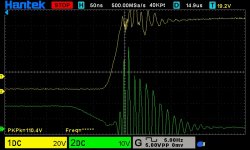

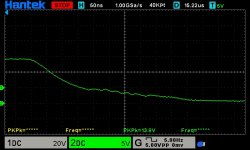

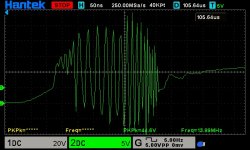

then moved to 50us pulse for 440A, here things get more interesting, Vds switch time is kinda sharp 50ns, at turn on the Vds as it drops down has a step on it in the miller plateau, but the Vgs instead of staying constant it shuts up rings a bit then drops down as previous the shot, the more odd thing is at turn off the Vgs drops nice and after miller clamp kicks in at 2v there is some crazy ringing, Vds goes up over shuts a bit then those ringings as in the Vgs, i don't know what to make of that, maybe is source inductance that rings and is seen on both Vgs Vds...

the 440A Vds Vgs shots

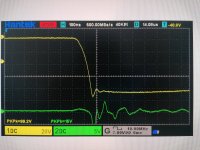

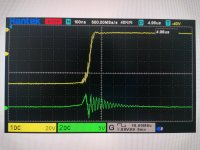

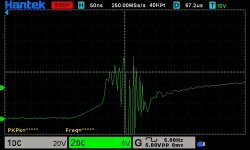

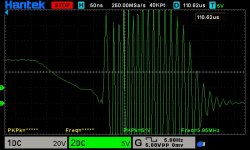

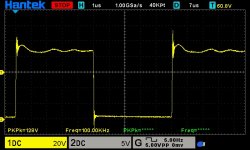

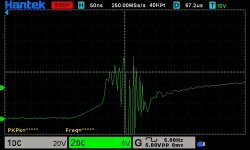

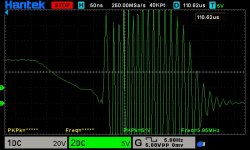

then chaged the Rgate 4.7R for Ton and Toff, and did 50us pulse for 440A, here the Vds switch time increased to 100ns and the ringing amplitude settled down a bit, but same behavior as before

the 440A Rg4,7R, Vds Vgs shots

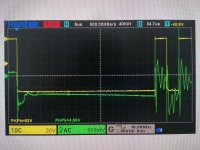

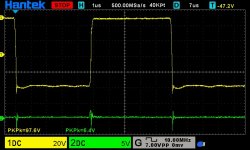

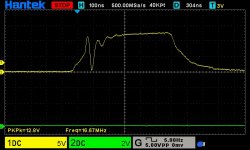

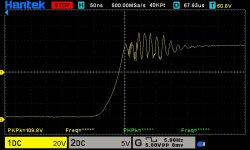

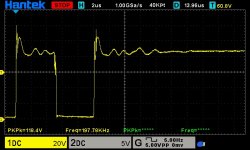

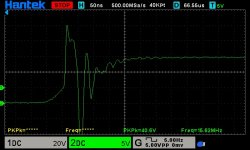

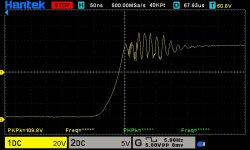

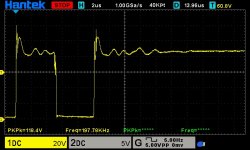

then did a 5us pulse for low current (about25A) to see is the ringing goes away, it shure did, but the turn on has the same odd drop...

Vgs shots

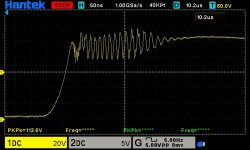

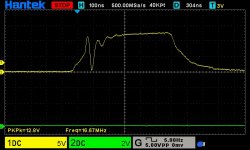

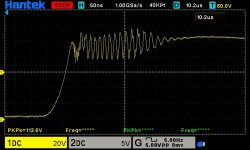

then moved to 100us pulse for 850A, here things get way crazy ringing, the desat did not trigger,i have to lower zenner voltage but i'l get to that after i sort tings out with ringing, the strange thing is that ringing occurs on gate just after Vgs gets to 2v and miller clamp kicks in

850A Vgs Vds shots

I tryed 10nf on gate placed between 1r and 4,7r resistors but made ringing way worst and longer lasting.

I did the 850A sevral times so it does survive that curent, i would like to go up to 1000A for just testing purpose, and to have confidence in the controller that it can handle A LOT of current, and from there down rate for a safe all day long 300A as nedded.

So 2 things i need to sort out: why is that dip in Vgs at turn on and why is that ringing after the turn off on Vgs.

Please fell free to show your thoughts on what i presented here.