I have a controller with a similar architecture, but it's small power H-Bridge (tested to 20A phase current at 25V). The current sensor is a 5mOhm resistor, placed between GND and the lower FET, and after the DC link caps. No small snubber caps at all, and very lazy layout in a single side PCB with some 2 inch traces from caps to FETs, with no overlaping planes at all (it's a single side PCB afterall). I don't find anything "fundamentally" wrong in the measurements I did so far, which kind of surprises me, but it is probably due to the low power.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

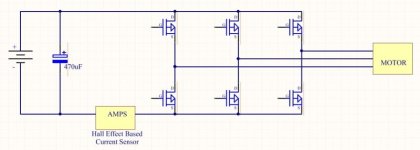

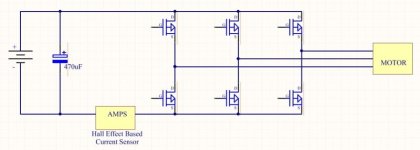

DIY 6FET Controller help

- Thread starter SjwNz

- Start date

HighHopes

10 kW

- Joined

- Mar 28, 2013

- Messages

- 929

Njay, you're talking about current sense in a differnt location than what we're talking about. what you describe is OK for low power application not needing high llevel of current measurement accuracy.

"placed between GND and the lower FET" is different between DC link cap and FET.

"placed between GND and the lower FET" is different between DC link cap and FET.

It's both, HH. GND -> cap-minus -> shunt -> n-fet source

https://github.com/vnevoa/DiffTrike...ridge/hw/bridge-power-schematics.pdf?raw=true (there are 1uF snubber caps but I never installed them, and there's only 1 N-FET not parallel of 2, with 100 Ohm gate resistor).

https://github.com/vnevoa/DiffTrike...ridge/hw/bridge-power-schematics.pdf?raw=true (there are 1uF snubber caps but I never installed them, and there's only 1 N-FET not parallel of 2, with 100 Ohm gate resistor).

Ok, because as I see it it's the same, except SjwNz put the impedance on the top rail while I put it on the bottom one.

(well, at the bottom it acts as a feedback limiting di/dt on the bottom FET while at the top... ehhh... humm... ok, I'll see what you have to say )

)

(well, at the bottom it acts as a feedback limiting di/dt on the bottom FET while at the top... ehhh... humm... ok, I'll see what you have to say

HighHopes

10 kW

- Joined

- Mar 28, 2013

- Messages

- 929

my "sense" was that OP was trying to do as shown on page 3 which in my opinion is not allowed. Njay is doing page 2 which is allowed but must be accepting of certain compromise. I am doing page 1 because my application & design spec requires.

Attachments

SjwNz

100 W

Will it make any difference if the sensor is placed on the Neg rail between FETS and CAPS, Same as your page 3 HighHopes but on the Neg Rail.

if its a issue on the Pos rail then I guess it will be a problem on the Neg rail as well.

I will probably go back to 3 sensors on the phase outputs as some time in the future I will see how much I can get out of my controller

and may be looking at phase currents around 100 to 150amps, so I don't want to upset the laminated bus impedance and cause extra voltage spikes

and other issues.

Njay, I used your method for a small controller I made for a friend to control landing gear on those Quad rotor flying things.

Thanks for all your info guys.

Going to try and have this running by the end of the year.

if its a issue on the Pos rail then I guess it will be a problem on the Neg rail as well.

I will probably go back to 3 sensors on the phase outputs as some time in the future I will see how much I can get out of my controller

and may be looking at phase currents around 100 to 150amps, so I don't want to upset the laminated bus impedance and cause extra voltage spikes

and other issues.

Njay, I used your method for a small controller I made for a friend to control landing gear on those Quad rotor flying things.

Thanks for all your info guys.

Going to try and have this running by the end of the year.

HighHopes

10 kW

- Joined

- Mar 28, 2013

- Messages

- 929

nice try, but no.

you can put just 2 of 3 current sensors on the AC ouput to save cost, but you have to use faster slew rate op-amps in the feedback circuit to compensate.... and they cost more $ so not sure how much you really save with 2 sensors. also, with just 2 sensors you will not be able to control circulating currents or zero sequence current nor will your controller perform well during high acceleration when system is unbalanced.

ok.. i will try to be more open minded. i will say this. if you put the current sensor in that location you will be leaving the world of "known & proven architecture" and entering an unproven and likely to fail world. its similar to arlo's idea of using the large drain tab to pass current, people have tried it and discovered in the end it wasn't a good idea. its possible that you (and arlo) will find a way to make it wonderful, to be absolutely ground breaking and will discover new architectures. but to be honest, you really need to develop a good working (funcitonal + reliable) basic inverter so you know what the standard is and WHY it is that way before you go off on your own tangent developing in your own style.

i say all that to be fair. i don't want to be the bringer of bad news "no, its bad" with no explanation. and i also don't want to stop you from exploring things. but, i do have wisdom in this field from years of hard work under the direct tutelage of world wide masters. i spent YEARS designing only gate drivers (before i moved in to systems) in high performance high reliability applications. i mean, anyone can say anything in a public forumn & make up any lie, but i've been at this on ES for over a year and at least one student has had very good success following my "rules". and now zombiess is off designing in their own style. and guess what, his new designs are looking good.

its not so easy to do a project like you are attempting properly. that statement is evidenced easily; look around the web, how many open source successful high power inverters are there (that are any good)? if it were easy, there would be thousands.. at least 100.. but, is there even 3? so take your time. learn the rules. learn WHY the rules are the way they are. design according to the rules. then, on your next inverter, use the rules more as a guideline and break the rules when and where it makes sense to do so (but make sure you fully understsand the impact of a rule broken).

you can put just 2 of 3 current sensors on the AC ouput to save cost, but you have to use faster slew rate op-amps in the feedback circuit to compensate.... and they cost more $ so not sure how much you really save with 2 sensors. also, with just 2 sensors you will not be able to control circulating currents or zero sequence current nor will your controller perform well during high acceleration when system is unbalanced.

ok.. i will try to be more open minded. i will say this. if you put the current sensor in that location you will be leaving the world of "known & proven architecture" and entering an unproven and likely to fail world. its similar to arlo's idea of using the large drain tab to pass current, people have tried it and discovered in the end it wasn't a good idea. its possible that you (and arlo) will find a way to make it wonderful, to be absolutely ground breaking and will discover new architectures. but to be honest, you really need to develop a good working (funcitonal + reliable) basic inverter so you know what the standard is and WHY it is that way before you go off on your own tangent developing in your own style.

i say all that to be fair. i don't want to be the bringer of bad news "no, its bad" with no explanation. and i also don't want to stop you from exploring things. but, i do have wisdom in this field from years of hard work under the direct tutelage of world wide masters. i spent YEARS designing only gate drivers (before i moved in to systems) in high performance high reliability applications. i mean, anyone can say anything in a public forumn & make up any lie, but i've been at this on ES for over a year and at least one student has had very good success following my "rules". and now zombiess is off designing in their own style. and guess what, his new designs are looking good.

its not so easy to do a project like you are attempting properly. that statement is evidenced easily; look around the web, how many open source successful high power inverters are there (that are any good)? if it were easy, there would be thousands.. at least 100.. but, is there even 3? so take your time. learn the rules. learn WHY the rules are the way they are. design according to the rules. then, on your next inverter, use the rules more as a guideline and break the rules when and where it makes sense to do so (but make sure you fully understsand the impact of a rule broken).

For the reasons of... ? If it is because that way limits what can be measured, I understand that, although my application is different, it's an h-bridge for a DC brushed motor. Pages 2 and 3 methods' drawbacks I see are 1) dissipative breaking current measurement cannot be done, 2) motoring phase current can only be measured during the ON time of the PWM (can be computacionaly hard to do, depending on your brain hw) and 3) the source impedance limits your di/dt (not a problem in my controller, maybe even a "blessing"). But maybe there is some reason from an electrical point of view, that's why I'm so interested in knowning. I'm re-spinning the controller (it's a < 500W h-bridge for a DC brushed motor) and planning on moving the sense resistor from page 2 (gnd - cap - resistor - fet) to page 3 (Vat - cap - resistor - fet), becasue I want to use a sense resistor amplifier and can't find one (at least not at mouser) that measures bidirectionally on the low side (looking to use this one: AD8418).HighHopes said:my "sense" was that OP was trying to do as shown on page 3 which in my opinion is not allowed.

HighHopes

10 kW

- Joined

- Mar 28, 2013

- Messages

- 929

you will limit the dc link capacitor's ability to do its job due to impedance in the path.For the reasons of... ?

My understanding is that HighHopes's evaluation is based on the professional experience with tons of tens of kilowatts, where any deviation from the best practices generate problems. And if at low power we do not follow the best practice, the problem is still there, but in a smaller extent. For example at <1000W a stray inductance may generate 0.1V in a small signal loop around (depending on the dimensions), and probably we can live with that, but at >10 kW that will be several volts that is not acceptable.

But in our case option 3 has some functional advantages as Njay says, so for me it worth to experiment with that. I'm not sure, but it looks like that it is similar in the Adaptto controllers that someone disassembled:

http://endless-sphere.com/forums/viewtopic.php?f=30&t=61484

http://endless-sphere.com/forums/viewtopic.php?f=2&t=61183&start=25

The sensor is not seen on the photos, but I've read somewhere it is a shunt (I can't imagine more than one sitting on that small board, but correct me if I'm wrong), and from the software they do sinusoidal drive and a lot of advanced controlling with that shunt only, including phase current and regen current control. Maybe not as accurate as FOC, but users look happy with that.

So I'm going to give a try to the layout on this picture, or something similar:

View attachment pcb.PNG

It is only a draft to show the connections, imagine beefy laminated overlapping tracks there.

R37 and R38 together is the shunt, and the trace would be the same in width. With this layout I can experiment the difference between with and without the shunt, because I can solder a copper plate in the place of the shunt. At least I can test at what voltage and current it makes any difference in the signals. If there is no big difference up to 100..150A, then it is fine for me. If it does not work well, I can still change to another current sensing method. At JU1,JV1and JW1 there is room for ACS758 sensors, I just don't have it in the library yet.

HighHopes, to clarify how the power bus laminating to each other should be, is it correct that it is required in order to cancel out the varying magnetic field that the high dI/dt generates? So the goal is to have opposite current directions on the 2 layers?

But in our case option 3 has some functional advantages as Njay says, so for me it worth to experiment with that. I'm not sure, but it looks like that it is similar in the Adaptto controllers that someone disassembled:

http://endless-sphere.com/forums/viewtopic.php?f=30&t=61484

http://endless-sphere.com/forums/viewtopic.php?f=2&t=61183&start=25

The sensor is not seen on the photos, but I've read somewhere it is a shunt (I can't imagine more than one sitting on that small board, but correct me if I'm wrong), and from the software they do sinusoidal drive and a lot of advanced controlling with that shunt only, including phase current and regen current control. Maybe not as accurate as FOC, but users look happy with that.

So I'm going to give a try to the layout on this picture, or something similar:

View attachment pcb.PNG

It is only a draft to show the connections, imagine beefy laminated overlapping tracks there.

R37 and R38 together is the shunt, and the trace would be the same in width. With this layout I can experiment the difference between with and without the shunt, because I can solder a copper plate in the place of the shunt. At least I can test at what voltage and current it makes any difference in the signals. If there is no big difference up to 100..150A, then it is fine for me. If it does not work well, I can still change to another current sensing method. At JU1,JV1and JW1 there is room for ACS758 sensors, I just don't have it in the library yet.

HighHopes, to clarify how the power bus laminating to each other should be, is it correct that it is required in order to cancel out the varying magnetic field that the high dI/dt generates? So the goal is to have opposite current directions on the 2 layers?

HighHopes

10 kW

- Joined

- Mar 28, 2013

- Messages

- 929

Peters, that is nearly exactly right.

for example

yes, canceling the fields. will it run "fine" if you make PCB with DC bus side by side instead? yes, probably up to 1kw before you notice strangeness. can you force it to work up to 10kw? maybe. but your noise will be so bad that you will make so much "fixes" and you will never pass an EMI scan so it could never be a commercial product.

perhaps more subtle.. if you make a bad architecture you will spend too much time on the bench fiddling to get it right. and secondly, any professional who sees your schematic/pcb will know instantly its value and know what it can and can not do. no marking BS like will fool them. but on the other hand, there are millions of bad and extremely bad controllers being sold every day with thousands and thousands of happy (and some really pissed) customers .

ps. my experience is with 1kW high performance to 80kw (this is continuous rating, typically 540V bus).

exactly. the higher power you go, the less margin you will have. there are advantages to what you propose, i'm not denying that. what i am saying is that any time you have to deviate from the norm, you must understand what the impact will be and how you can live with that.and probably we can live with that, but at >10 kW that will be several volts that is not acceptable.

for example

you will not get anywhere near the quality of torque control with shunt measurement. and furthermore, it is VERY inefficient (drains your batteries). so would you call that "advanced"? i wouldn't; i'd call it cheap & wasteful. doesn't mean you can't be happy with it though.they do sinusoidal drive and a lot of advanced controlling with that shunt only

yes, canceling the fields. will it run "fine" if you make PCB with DC bus side by side instead? yes, probably up to 1kw before you notice strangeness. can you force it to work up to 10kw? maybe. but your noise will be so bad that you will make so much "fixes" and you will never pass an EMI scan so it could never be a commercial product.

perhaps more subtle.. if you make a bad architecture you will spend too much time on the bench fiddling to get it right. and secondly, any professional who sees your schematic/pcb will know instantly its value and know what it can and can not do. no marking BS like will fool them. but on the other hand, there are millions of bad and extremely bad controllers being sold every day with thousands and thousands of happy (and some really pissed) customers .

ps. my experience is with 1kW high performance to 80kw (this is continuous rating, typically 540V bus).

HighHopes

10 kW

- Joined

- Mar 28, 2013

- Messages

- 929

one other thing.. i should premise my comments that i am talking about building one-off controllers. where spending $30 extra to make is "good" is worth it.

if you were designing for a commercial product, you might still do the same, but you would spend a lot more time optimizing so that you spent only the exact $ you MUST spend. and also you would go through a round of designing for manufacture so that it is cheap to layout and assemble.

if you were designing for a commercial product, you might still do the same, but you would spend a lot more time optimizing so that you spent only the exact $ you MUST spend. and also you would go through a round of designing for manufacture so that it is cheap to layout and assemble.

But that impedance is also there if using the shunt on the low side, and you mark it "acceptable"; that's what I'm not understanding. The only difference I see is because on the low side it acts as a feedback limiting di/dt (my fet driver source connection currently goes to gnd, there is, to the dc link caps, and not to the fet's source).HighHopes said:you will limit the dc link capacitor's ability to do its job due to impedance in the path.For the reasons of... ?

Ok.HighHopes said:so would you call that "advanced"?

By advanced I mean with the plenty of functionality implemented in the firmware they got the most out of a simple hardware, I can appreciate it.

HighHopes

10 kW

- Joined

- Mar 28, 2013

- Messages

- 929

if you put the sense resistor shunt on the low side mosfet, you will have far less common mode voltage problem than if you tried to put it on the high side.

also, the edge rate (frequency) of the DC link capacitor current is extreme, easily into the megahertz. so insertion impedance matters to the quality operation of the H-bridge. diode reverse recovery needs that fast current, it will not tolerate being slow. but not only that, the sensor and its associated low voltage analog signal conditioning must be capable of managing such high frequency (which hall effect current sensors are not so good at). so if you wanted shunt resistors in your design, you need slow switching mosfets and slow reverse recovery diodes and over filtering of analog current measurement which all equals low(er) performance (less bandwidth in your torque control).

anyway, its up to you so do what you like. if it works for you then great, but don't be surprised if you have a hard time taking such a design to higher power levels. if it doesn't work, or you have "mysterious" problems in your system under operation even at light loads, or works totally fine for 8 months and then catastrophic failure as your component's life has been used up way too fast.. well, least you know where first to investigate.

also, the edge rate (frequency) of the DC link capacitor current is extreme, easily into the megahertz. so insertion impedance matters to the quality operation of the H-bridge. diode reverse recovery needs that fast current, it will not tolerate being slow. but not only that, the sensor and its associated low voltage analog signal conditioning must be capable of managing such high frequency (which hall effect current sensors are not so good at). so if you wanted shunt resistors in your design, you need slow switching mosfets and slow reverse recovery diodes and over filtering of analog current measurement which all equals low(er) performance (less bandwidth in your torque control).

anyway, its up to you so do what you like. if it works for you then great, but don't be surprised if you have a hard time taking such a design to higher power levels. if it doesn't work, or you have "mysterious" problems in your system under operation even at light loads, or works totally fine for 8 months and then catastrophic failure as your component's life has been used up way too fast.. well, least you know where first to investigate.

zombiess

10 MW

HighHopes said:if you put the sense resistor shunt on the low side mosfet, you will have far less common mode voltage problem than if you tried to put it on the high side.

Is this because the differential of the noise with regards to it's reference level, reverse recovery currents?

What happens if you balance out the paths and placed an identical resistance in the upper path, does this improve things (not as good as proper placement).

I'd also be concerned about a hall type sensor being placed out of the laminated buss (altering it's path as one of the layouts on here showed). Shunt type could place the sense resistor on the laminated bus, but it's still not physically balanced and that seems incorrect due to non symmetry (at least for high power or reliable operation is required).

Does the small sense resistor between the dc link now form a low pass RC network? If so could this create higher amplitude harmonics on the bus between DC link to MOSFET than would otherwise naturally exist (less spectrum since they are now all forced to be low passed w.r.t. the RC network)?

Hopefully that makes sense, hard to describe what I'm thinking about. I'm in left field.

zombiess

10 MW

peters said:My understanding is that HighHopes's evaluation is based on the professional experience with tons of tens of kilowatts, where any deviation from the best practices generate problems. And if at low power we do not follow the best practice, the problem is still there, but in a smaller extent. For example at <1000W a stray inductance may generate 0.1V in a small signal loop around (depending on the dimensions), and probably we can live with that, but at >10 kW that will be several volts that is not acceptable.

But in our case option 3 has some functional advantages as Njay says, so for me it worth to experiment with that. I'm not sure, but it looks like that it is similar in the Adaptto controllers that someone disassembled:

http://endless-sphere.com/forums/viewtopic.php?f=30&t=61484

http://endless-sphere.com/forums/viewtopic.php?f=2&t=61183&start=25

The sensor is not seen on the photos, but I've read somewhere it is a shunt (I can't imagine more than one sitting on that small board, but correct me if I'm wrong), and from the software they do sinusoidal drive and a lot of advanced controlling with that shunt only, including phase current and regen current control. Maybe not as accurate as FOC, but users look happy with that.

So I'm going to give a try to the layout on this picture, or something similar:

It is only a draft to show the connections, imagine beefy laminated overlapping tracks there.

R37 and R38 together is the shunt, and the trace would be the same in width. With this layout I can experiment the difference between with and without the shunt, because I can solder a copper plate in the place of the shunt. At least I can test at what voltage and current it makes any difference in the signals. If there is no big difference up to 100..150A, then it is fine for me. If it does not work well, I can still change to another current sensing method. At JU1,JV1and JW1 there is room for ACS758 sensors, I just don't have it in the library yet.

HighHopes, to clarify how the power bus laminating to each other should be, is it correct that it is required in order to cancel out the varying magnetic field that the high dI/dt generates? So the goal is to have opposite current directions on the 2 layers?

Your bus inputs should overlap each other as much as possible all the way and then twist the input wires. You can reduce the inductance of the layout by rotating the capacitors pints so they are inline with each other. This can significantly reduce produced noise. The paths should be symmetrical. Not sure if there would be an improvement in the layout by keeping the entire bus inline and overlapped vs the 90 degree dog leg you force the current to take. HH can probably answer that one better.

Why place the battery current sense resistor in that location, what is your justifications? There are many reasons to not place it there but how many reasons are there to put it there?

What control brain do you plan to use with this? I don't see any current sensors for the phase current.

HighHopes

10 kW

- Joined

- Mar 28, 2013

- Messages

- 929

my experience is not with making something as cheap as possible. it is with performance & reliability. the customers i had demanded that, so that's what was delivered. if the design was for consumer product fabbed out of china, perhaps i would have learned all there is to making things cheap; but i didn't.

is there a way to make the current sensor work if placed between the DC link cap and the mosfet bridge? i don't think so. but if you want to do it for cheapness sake, go for it. your power level is low so maybe it will be OK in the end. if it does work or does not, please post your results here so we can all learn something new.

is there a way to make the current sensor work if placed between the DC link cap and the mosfet bridge? i don't think so. but if you want to do it for cheapness sake, go for it. your power level is low so maybe it will be OK in the end. if it does work or does not, please post your results here so we can all learn something new.

zombiess said:Your bus inputs should overlap each other as much as possible all the way and then twist the input wires. You can reduce the inductance of the layout by rotating the capacitors pints so they are inline with each other. This can significantly reduce produced noise. The paths should be symmetrical. Not sure if there would be an improvement in the layout by keeping the entire bus inline and overlapped vs the 90 degree dog leg you force the current to take. HH can probably answer that one better.

Why place the battery current sense resistor in that location, what is your justifications? There are many reasons to not place it there but how many reasons are there to put it there?

What control brain do you plan to use with this? I don't see any current sensors for the phase current.

With the resistor in this location I can detect cross conduction in microseconds. This is an alternative to desat, that I don't plan to use, because I prefer a more simple gate driver. If I put the resistor before the DC caps, the detection is delayed and the charge in the caps may kill the MOSFETs. And the supply current is the average of the resistor current, so I don't need another shunt.

To me it looks like the inductance is more a problem in the DC supply line than a few mOhm resistor. There are special low inductance current sense resistors for this purpose, but an ACS sensor would probably have too much inductance.

For brain I'm going to try a dsPIC33:

http://endless-sphere.com/forums/viewtopic.php?f=30&t=44910&start=150

In my current boards I use Atmel, but Microchip has more choice of components.

After considering the options and viewing zombiess's design in more details, I made another drawing yesterday, but I did not decide yet which one I want to build.

I hope SjwNz will not mind if I post here, this is also a 6FET controller.

The top MOSFETs are at the top edge of the board and all the power layers are in the middle section.

View attachment top.PNG

View attachment bottom.PNG

View attachment power.PNG

Board outline is the light blue.

Bottom layer is green (output signals), top is red (GND), and the power layer between them is the purple(+Vbat).

MOSFETs and phase current sensors are on the bottom side.

Four capacitors are on the right, layed horizontally, because I want the height to be as low as possible. These are 4x 1000uF 100V 22mm diameter, 30mm long snap-in capacitors. One leg is soldered on the bottom side (that is the purple at this part, just the pads are green, because it was not possible to move a pad in a middle layer...), the other leg is on the top side of the board. Dimensions of this board are mostly constraints.

The complication here is that it needs a 3rd copper layer to connect the high side sources to the low side drains.

My concern is that the power supply lines are quite long along the board, that is some inductance, perhaps 50..100nH or more. Ok, the reverse currents cancel the field, but to what extent...? And maybe there are other things to consider.

What do you think, guys?

I hope SjwNz will not mind if I post here, this is also a 6FET controller.

The top MOSFETs are at the top edge of the board and all the power layers are in the middle section.

View attachment top.PNG

View attachment bottom.PNG

View attachment power.PNG

Board outline is the light blue.

Bottom layer is green (output signals), top is red (GND), and the power layer between them is the purple(+Vbat).

MOSFETs and phase current sensors are on the bottom side.

Four capacitors are on the right, layed horizontally, because I want the height to be as low as possible. These are 4x 1000uF 100V 22mm diameter, 30mm long snap-in capacitors. One leg is soldered on the bottom side (that is the purple at this part, just the pads are green, because it was not possible to move a pad in a middle layer...), the other leg is on the top side of the board. Dimensions of this board are mostly constraints.

The complication here is that it needs a 3rd copper layer to connect the high side sources to the low side drains.

My concern is that the power supply lines are quite long along the board, that is some inductance, perhaps 50..100nH or more. Ok, the reverse currents cancel the field, but to what extent...? And maybe there are other things to consider.

What do you think, guys?

The inductance between a FET and the exit point to the phase should be tiny; phase current switches between the phase exit point and both FETs, meaning will put those 2 inductances to work (top fet - exit point and bottom fet - exit point). Why not bring both FET rows closer and move the current sensors to the phase board exit points at the board's bottom?

zombiess said:What control brain do you plan to use with this? I don't see any current sensors for the phase current.

It can be measured, during the ON time of the PWM cycle, I do that too. In that period, the current going through the shunt is the same going through the phase.

Alan B

100 GW

Is the shunt bandwidth adequate to make these high frequency measurements accurately?

Similar threads

- Replies

- 4

- Views

- 874

- Replies

- 27

- Views

- 918

- Solved

- Replies

- 21

- Views

- 1,271

- Replies

- 17

- Views

- 1,584