SjwNz

100 W

I hope SjwNz will not mind if I post here, this is also a 6FET controller.

No worries peters

I hope SjwNz will not mind if I post here, this is also a 6FET controller.

Ok, I see, I also did not like the sensor placement. I made 2 other layout options, but the sensors are at the top edge of the board, because it was better to connect, and the big capacitors are on the left.Njay said:The inductance between a FET and the exit point to the phase should be tiny; phase current switches between the phase exit point and both FETs, meaning will put those 2 inductances to work (top fet - exit point and bottom fet - exit point). Why not bring both FET rows closer and move the current sensors to the phase board exit points at the board's bottom?

zombiess wrote

Layout is a very difficult challenge. I now prefer external sensors for flexibility in mounting.

zombiess said:Peters,

Have you calculated the required DC link capacitance and current ripple required for your controller? If not, doing so will allow you to choose the appropriate capacitors. Putting non justified caps for DC link can be a recipe for disaster.

HighHopes posted a great PDF he wrote on calculating the DC link size and requirements with all the needed math formulas. If you can't find it I can post a copy I have later.

What MOSFET, max operating voltage/current and switching freq are you thinking of?

I suspect you might be OK with a 20-30uF cap of the proper type, but the math must be done. Electrolytic a are something you should probably stay away from for DC Link usage.

Do you have a 3rd dimensional size limit?

If you place your current sensors in that location, just remember that you should not have any gate driver traces or circuitry overlapping anything in the power pass. This becomes really important over a 1-3 kW.

Layout is a very difficult challenge. I now prefer external sensors for flexibility in mounting.

I've never heard this before and it doesn't make much sense. What type of capacitor, there are lots of types with different properties, what ESR, what frequency, what charge level, etc? Datasheets make a lot more sense.the rule of thumb is 10..20mA/uF, but better to look in the datasheets in every case

No, it can be acceptable only if the power supply has a very low output impedance, for example the big capacitors are placed at the output of the power supply. But it is not our case, because the battery has the ~0.1 Ohm resistance (more or less). So in our case the purpose of the DC link capacitor is to filter the DC bus current from the PWM frequency and to keep the ripple voltage low.zombiess said:The main purpose of the DC Link is to supply current to the circuit until the battery/power source is able to catch up and supply current due to the inductance in the power feed, which means twisting the battery feed wires is a good idea to lower their inductance.

I found HighHopes PDF for DC-Link caps.

viewtopic.php?f=30&t=31804&start=50#p839118

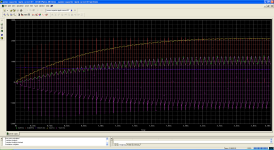

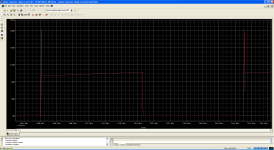

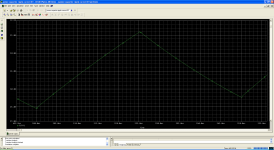

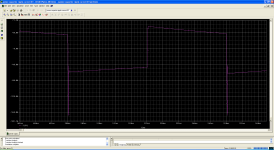

The glitch at the rising edge is only the reverse recovery current of the low side FET body diode (not sure if it is accurate in the pspice model of the FET).

Ok, but our calculations are fundamentally different, and the result for the needed capacitance can differ by 10 times multiplier...HighHopes said:FYI, that post was not meant to be a definitive guide to calculating an optomized uF value of DC link cap. we were discussing the merits of electrolytic cap vs. poly cap and my position was that poly is way better (type MKP). the post was meant to show how a poly cap is NOT more expensive than an electrolytic capacitor in this application and will take up less volume and perform better. i used some math to make my point. mind you, if you had no other way to estimate what uF cap you want, the document will get you in the ball-park, but its not meant to be super accurate.

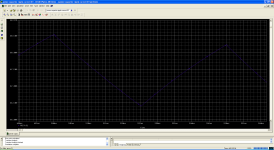

Then we add some high frequency oscillations. As you said above, the simulation with inductances can be different from real measurements, and I think it is because the real supply lines are distributed parameter transmission lines, especially when the power bus planes are laminated to each other. That is not only a reduced inductor, but has an increased distributed capacitance. This could be modeled with a lot of small LC circuits.Njay said:ehhhh... how about adding at least bat wire inductance and the already mentioned cap ESR, plus cap ESL?

Ok, It's good to knowHighHopes said:ps. silicon carbide mosfets do not exhibit any reverse recovery behaviour

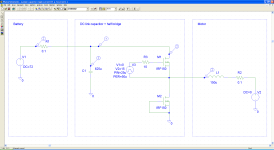

No problem, I attached the file. It is made for PSpice v9.1 student edition, it is not a new version, but I think still widely used.zombiess said:Peters, thanks for posting the simulation. Do you mind sharing the PSpice file?

I think I see what you are trying to show in your example.

BEMF is simulated by the voltage source in the motor model. Now it is set to 0, but can be any other. When the voltage is higher than duty_cycle*72V, then there is no effective motor current. That would be regenerative braking for which the low side FET should be switched, too.What happens when the load becomes very dynamic such as spinning motor where you have an inductor moving in a magnetic field generating BEMF?

I don't exacty know its effect. If they introduce some torque and current ripple, and its frequency is lower than PWM then it would be compensated by the current control loop.What about multiple magnet poles and stator teeth?

I suppose the mechanical transients are usually slower than PWM, so the control loop should limit the max. current. If there is a very fast transient, then the current may increase for a while. Or if the current control loop is slow, then there would be a current overshoot for some time, but that is not a good design.Different operating conditions the motor experiences such as sudden acceleration (like wheel slip), regen, sudden stopping such as locking the rotor like a panic stop.

Operating load conditions?

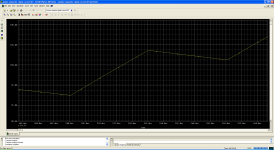

Yes, definitely. I calculated only the most simple case. For 3 phase I did not dig into the details, but for simple trapezoidal drive it must be the same, because one phase is switched at a time in every 6 commutation states. This is for unipolar PWM. At bipolar PWM the overall switching frequency on the bridge input is the double of the PWM, so the needed capacitor is maybe the half of the calculated, this could be checked by simulation, but I've read somewhere it adds harmonics to the motor current and reduces efficiency. In 4-quadrant drives it is probably more complex, because there is reverse current from the motor to the capacitor in every PWM cycle.Does being 3 phase vs single phase AC on the output change how it behaves?

I was thinking more on the sinusoidal case, and now I find possible that HighHopes's formula is the correct one for the fully symmetrical sinusoidal drive, and mine is not applicable in this case

HighHopes said:btw peters, you might be interested in my post #2 over here http://ivanbennett.com/forum/index.php?topic=112.0

Alan B said:The infineon chips are unobtanium, so I'll probably go with a different one, perhaps the ACPL-333J that has been discussed.