Futterama

1 kW

So you put in an IC between the dsPIC and the gate drivers? Which one?

I decided for initial testing I wanted to use a latching shut down

I put one at each location due to symmetry. I'll gladly drop to a single G-S cap/resistor if you think it's ok. I could place it right after the gate resistor.

HighHopes said:this comment comes from arlo's thread but i didn't want to continue discussion of your design over there..

on the subject of parallel mosfets and pull-down resistor & G/S caps.

I put one at each location due to symmetry. I'll gladly drop to a single G-S cap/resistor if you think it's ok. I could place it right after the gate resistor.

if you have ONE G/S cap or one per mosfet, it is NOT symmetric to put one cap per mosfet. think of it as putting 5nF per mosfet. if you measured each cap, maybe the first one is 4.98nF, the second is 5.5nF, the third is 5.0nF.. etc. is it still symmetric? no.

but if you have just ONE G/S cap, 30nF,es.. and you measure it to find in reality it is actually 31nF, is the design still symmetric? Yes.

remember, it is from the view point of current sharing in parallel mosfet that we make this discussion. the more the design encourages symmetry, the better.

Jasmine said:Dear Zombiess, you must be a considerate person who is professional, I like your talking!

i have learned that measuring D/S voltage is not that useful other than to get a sense of how fast the switching is. i don't even look at how much ringing there is because the frequency is so high i can not trust that it is real (i.e. would it dissapear if i removed the probes?).

keep the gate resistor within the range acceptable to the mosfet datasheet

start with the highest resistor, maybe 20 ohms (but read you're datasheet) if heating of mosfet is acceptable at highest gate resistor then you're done. we don't worry about D/S switching speeds because gate resistor is WITHIN datasheet parameters so your worse case deadtime calcs are still valid. D/S switching speeds then are as slow as it can be for this mosfet and we pray it is slow enough to not suffer from noise problems. but its a good prayer because we build the inverter with quality parts, laminated bus-bar, structured approach to gate driver design & layout so we know our system can handle some noise without difficulty.

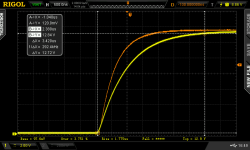

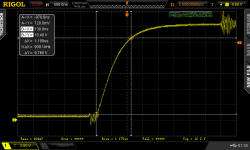

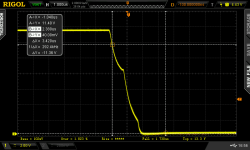

that's really important. teh gate resistor (and maybe G/S cap if you need it) are there to find the balance between mosfet heating and noise generated. so when you have error detection giving false trigger when D/S switching is fast and no error when D/S switching is slow, this is a good sign that you have found where your limit is. in my experience switching DC bus voltage in < 200ns means you will have a lot of noise likely more than what a standard gate drive design can manage. and from what i know of MOSFETS they are designed to switch fast which is not exacty the same as IGBT. so perhaps your instincts of switching speeds and how to achieve them (gate resistor + gate cap) so avoid noise problems is good.. seems the right path to me. make sure you can manage the heat rise, and you're done.I noticed I was having some odd false triggers from my error detection circuit which would shut down the PWM

HighHopes said:as a side note, i did notice your mosfet has an internal gate resistor value of 2.7Ohm which may imply you do not need the external 0.5 Ohm and also makes me wonder if your spreadsheet math for calculating gate drive parameters & sizing takes this into consideration? if you put external 10 ohm for example, the internal represents almost 30% addition.. could make a noticable difference in your math.

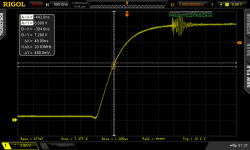

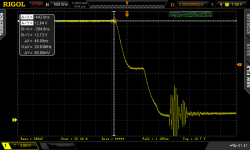

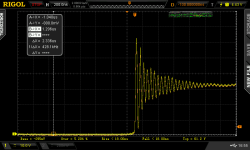

Lebowski said:The 20-22 MHz looks like the typical ringing of the mosfets output cap with the power line inductance. Place 10nf across each cet and you'll see the frequency change...

Njay said:it's a typo... fet.

Njay said:Drain to source. Leb is saying to artificially increasing the "fet output capacitance" to test the hypothesis that the ringing comes from it, by seeing a change in the ringing frequency (which should be lower with the 10nF cap).

HighHopes said:hmm... G/S cap present or not should not cause your PIC fault monitoring chip to false trigger. maybe it is Real trigger? i think you should look into this more.

if i remember the PIC's job is to latch a gate drive IC fault and shut down PWM? when PIC false trigger, what does the fault pin look like on the gate drive IC (brain board side). what does this same signal look like when measured at the PIC chip (theoretically should look the same)? is there noise here?

what is this Albis chip?Everything it opto coupled except the phase outputs which go into the Albis controller chip

yes, but look at the massive RC fillter i have in front of it. the fault has to be present for a good long time before the latch detects so i do not latch on noise. i do not need to detect immediate, the gate drive does that. sorry i didn't mention that in your schematic review. too many details!I looked at your schematic, looks like you are using a derivative of the same transceiver chip I am. 74???245??? bidirectional with enable pin to shut down your PWM output.

HighHopes said:what is this Albis chip?Everything it opto coupled except the phase outputs which go into the Albis controller chip

yes, but look at the massive RC fillter i have in front of it. the fault has to be present for a good long time before the latch detects so i do not latch on noise. i do not need to detect immediate, the gate drive does that. sorry i didn't mention that in your schematic review. too many details!I looked at your schematic, looks like you are using a derivative of the same transceiver chip I am. 74???245??? bidirectional with enable pin to shut down your PWM output.

Everything it opto coupled except the phase outputs which go into the Albis controller chip

HighHopes said:deadtime is the difference betweeen longest time OFF and shortest time ON.

see my two or three posts on arlo's thread, March 16. your datasheets might not have all this information needed so take some guesses based on similar. what is variation due to gate resistance? as we discovered, mosfet datasheet doesn't go into it, but for sure there is an effect. you have practical experience that can be used here to make some guess. the more guesses you make the more your safety margin adder has to be (compensate just incase your guess is bad).

http://endless-sphere.com/forums/viewtopic.php?f=30&t=35387&start=1225

my gut feeling tells me a deadtime around 1us is "about right" for your power level and components.

PWM processing 0.8 on / 3.9 off

Isolation delay 25 on / 100 off

Gate driver delay 350 on / 620 off

Gate driver distortion 25 min / 120 max

Mosfet delay 18 on / 41 off

Mosfet rise/fall 73 on 39 off

Fastest on time, 466.8nS

Slowest off time, 803.9nS

Difference between fastest on and slowest off time = 337 nS.

33% safety margin = 337 * 1.33 = 448nS.

Closest setting in Lebowskis controller, 500nS